| |

|

Главная

>

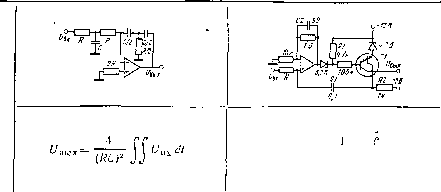

Аналоговая интегральная схема Специализированные Найме нова C мирующиА интеграто1 нфференциальнь(Я интегратор*! Ь я к] и - *> При включении генераторов гокт J\ и /а в есто генераторов напри леннп От , и *1 В - коэффиЕ иеит усиления базопгго тока 7/, CailO пФ устраняет Сс1Моволч>жяе ОУ близчо К н>л!0, а токи во входпон цепл и цепи ОС /<, прибпн-зительно равны т е V,J-R,~V, ,>{\pC) паи V {i)-{\iRC)\V di. Основные состазляющие ошибок интегрирования сбусювчепы иапр!1жением смещения н>ля (Ум и входными токами /м, /р ОУ. Прл (У,;;. =0 входные токн ОУ протекают через конленсатор заряжая его Обусловленное этим напряжение ошибки складывается с (Уем и приводит к появлент1Ю линейно изченяющеися составляющей выходного напряжения, которая при t- ос приводит к нарастанию выходного напряжения ОУдо максима пьноильеличины даже при О Если заземлить неинвертир>ющий вход ОУ через резистор R2, то иа погрешность интегрирования будет влиять только разность входных токов ОУ, которая обычно в 3-5 раз меныпе /рм (табл i 3) Выбирая сопротивления резисторов RI и R2 из условия R, = Ry Vcmv -южно практически исключить и влияние гУсч 14] Для интегратора, построенного иа ОУ с однопопюсной АЧХ, передаточная функция при Rj. R = R имеет вид аналоговые интеграторы Таблица 31 Двойной интегратор Интегратор с большой посгояннои зре-eни  рч -вых - Q J (2 -fi) <it-ьие К - выбирается нз \стовия IItV ыт=0 Переходная характеристика реального интегратора в отличие от идеального не является абсолютно линейной, хотя и весьма близка к линейной иа большей части переходного процесса. Учитывая, что /Си > I и обычно KuRC > получаем /Су /?с Отклонение реальной переходной характеристики от идеальной проявляется особенно сильгю в начальный люмент интегрирования (из за конечного быстродействия ОУ) и в области больших значений времени из за конечной величины Ки Наилучшая точность интегрирования достигается, когда время интегрирования < KuRC, а амплитуда сигнала на выходе интегратора (Увых < ъКи- Как видно из табл 3 i, ф>нкцнона тьные возможности базовой схемы интегратора (рис 3 3) можно сущ,ественно расширить, изменяя вид цепи ОС [5-71 Аналоговые интеграторы со сбросом. Из-за нендеа тьности ОУ выходное напряжение интегратора, дотнгн>тое в процессе иите- грирования, не уменьшается до нуля прн последущем нулевом входном сигнале, а продолжая изменяться, достигает максимального значения. Последнее делает практически невозможным правильное интегрирование последующих сигналов Для устранения этого эффекта выходное напряжение интегратора периодически сбрасывают до некоторого заданного уровня. В простейшем интеграторе для сброса используется аналоговый ключ на базе MДП-тpaнsиcтopa (рнс. 3 4) В режиме сброс (ключ замкн\т) задаются начальные условия интегрирования. Ключ увеличивает начальную ошибк\ интегрирования на (/ = Овхот- где г - о сопротивление открытого АШП-транзис-тора В режиме интегрирования МДП-транзистор закрыт и вносит ошибку из-за Рис 3 3 Простейший конечной величины сопротивления Грдд в аналоговый интегратор закрытом состоянии, заряда конденсатора С токами утечки МДП-транзистора и передачи части управляющего сигнала в цепь интегрирования. Преобладает в суммарном токе утечки МДП-транзистора обычно ток утечки перехода сток - исток (да вых/ раэ) Уменьшить утечку сток-исток, можно, используя двухтраизи-сторн>ю цепь сброса (рис. 3 5). Напряжение сток-исток (Уи о-ч: €if рос 0/,+ Он R1 CSpgff о о Рнс 3 4 Интегратор со сбросом Рис 3 5 Уменьшение влияния тока утечки перехода сток - исток Т2 транзистора TI в режиме интегрирования уменьшается до величины ()ц Ur2 = BHvapaa Следовательно, ток утечки между стоком и истоком TJ будет .меньше в Ip.JR Р в схеме на рис. 3.4. Основные разновидности интеграторов со сбросом приведены в табл. 3 2 [8, 9] Оптимальное сочетание точности и быстродействия имеет последняя схема в табл. 3.2, работу и наладку которой целесообразно пояснить.

|