| |

|

Главная

>

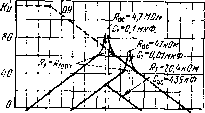

Аналоговая интегральная схема Разновидности интеграторов со сбросом Характеристика Структура Условия работц Запомяна 1С1Ций {уни- версаль ность, быст родействие) Интегрирование KI К2 замкнуты, КЗ разомкнут. Запоминание К1. К2 КЗ разомкнуты Сброс КЗ замкнут RC выбирается нз условия RC > 10 Свых-тях/ С автоматическим сбросом (быстродействие)  при UsbiX<fjlux bl-f (n-l)t/cr Ha базе 0У2 построен регенераторный компаратор (см. гл 7) С пернодн веским уст ранением ошибки (точность) Lib 4 Принципы проектирования и работы даиы в п 1 2 1 С непрерывной вы боркой и автоматическим сбро сом резуль тата интегрирования [(быстродей СТА не, точность) 78SH Fi ~ рдг7 fjiL5>lijitj Выходное напряжение равно сумме интeгpиpyвroгo сигнала и предыдущего сброшенного до нуля, в результате чего на выходе остается проинтегрированный новый сигнал Устройства выборки ~ хранения (УВХ) (см. гл. 7) поочередно осуществляют выборку и хранение предыдущего значения проинтегрированного в.ход-ного сигнала. Хранимое напряжение подается на вход схемы, в результате чего происходит непрерывный сброс в течение всего времени интегрирования. В качестве ключей УВХ могут использова гься либо две пары дополняющих МДП-транзисторов с одной шиной управления по цепи затворов, либо любые другие МДП-транзнсторы, нос разделенными цепями управления. При переключении транзисторов функции УВХ меняются. Интегрирующий блок 0У1 построен в виде обычного интегратора на базе ОУ типа 153УД5, имеющего малый др£Йф параметров В течение времени интегрирования проинтегрированный сигнал по цепи ОС (через 0У2) подается в суммирующую точку 0У1, осуществляя тем самым сброс интегратора. Тем временем происходит интегрирование вновь поступившего входного сигнала и его Запоминание в открытом УВХ. Калибровка схемы осуществляется сначала при разомкнутой ОС подбором сопротивления RI так, чтобы получить необходимую скорость iiapacia-пия выходного напряжения 0У1. Затем замыкается ОС и подбирается сопротивление R2 из расчета минимальных искажений выходного сигнала при ступенчатом входном Погрешность интегрирования такой схемы достигает О, [п, но может быть уменьшена иа порядок прн отрегулированном напряжении смешения нуля ОУ. 3.3. Аналоговые дифференциаторы Уравнения, описывающие функционирование простейшего аналогового ди4)4еренциатора (рис. 3.6) на базе идеального О, записываются исходя из равенства /j. = /c (i = О, Сое 0)- U,JR = -V,J{\!pC,l и,,(0= ~R, C,dV ldL Статические ошибки определяются в основном t/M н входными токами ОУ. С повышением частоты возрастает усиление дифференциатора и увеличивается составляющая ошибки из-за внутренних шумов ОУ (6/в fix Rf eRCp). Дифференциатор имеет АЧ.Ч двухполюсную с нyлe[, что указывает на возможность его самовозбуждения и появления динамической ошибки из-за колебательного переходного процесса. KpoNje этого, входной импеданс дифференциатора имеет емкостный характер и, следовательно, на высоких частотах может увеличиваться ток, отбираемый от генератора сигнала, что меняет условия работы последнего, если его выходное сопротивление недостаточно мало. Входной импеданс дифференциатора можно увеличить, включив последовательно с конденсатором С/ резистор RI Уменьшение влияния шумов и улучшение стабильности схелш можно достичь, шунтируя резистор Roc конденсатором Сое. Ниже приведен анализ влияния конечной полосы пропускания ОУ, резистора RI п конденсатора Сс на динамические характеристики дифференциатора, Рис. 3 6. Простейщий аиало-говый дифференциатор Прн однополюсной АЧХ Оу ((ор = 1/Т = gJjJКц) выходное напряжение дифференциатора, оперирующего с лиЕ1ейно-нарастаюш.ими напряжения- iP), записывается в виде [10] 7 Roc 1 Так как справедливо неравенство Wx/ZocCi > У2{Яо(С{}], то вторым слага1?чым можно пренебречь Поэтому переходной процесс выходного язпра-жения имеет вид, характерный для колебательного звена с собственной чзс-  Рис 3.7. Передаточные >:арак1ернстнкц дифференциатора тотой колебаний сОд = (/ocCi/ °= (tjij-w) к временем их затуха-1,ия 1э {U2T + i/2/?oe.fM-: X рхр Г Roc С, (3.1) Фазовый сдвиг входного сигнала достигает 180° на частоте UI3, передаточная характеристика имеет выброс (рис 3.7). а дифференциатор склонен к самовозбуждению. При включенном в схему рис. 3,6 резисторе R1 ОС ОС -1 Выброс при переходном процессе будет отсутствовать, если равны полюса Этой передаточной функнии 10], г е, ({HjRIR) = 4uJy(/?L,cCj). Отсюда следует, что оптимальная величина RI равна где Ки ((йд) - Коэффициент усиления ОУ на частоте cOg, В этом случае переходная характеристика при = равна Ув. (Г- -kRoc Ci !i--(l О ехр( -Шз О]- - (3-2) Если < щцт, то выражение (3.2) принимает вид (3.1) и время затухания = 2R,yiiifRi Tg В этом случае большой входной импеданс можно получить, увеличив сопротивление /?ос и пропорционально уменьшив емкость С/, чтобы оетавалась постоянной (очевидно, что значение /jout также

|