| |

|

Главная

>

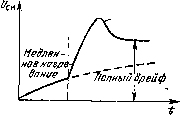

Аналоговая интегральная схема практический интерес представляет определение параметров ОУ, при ко 1ых можно пренебречь усилением синфазного сигнала. С этой целью запг м выражения коэффициентов усиления ОУ в обоих включениях с учето- 14) и (1.15), полагая для простоты вых = О (Т- е- ых = вых)- Тогда ч инвертирующего включения цля неиниертирующего включения . последних выражений видно, что усилением синфазного сигнала мояно енсбречь, если выполняются следующие условия соответственно для инвер-рующего и неинвертирующего включений: Неравенства (I.IG) показывают, что з инвертирующем включении вели-на синфазного сигнала и его усиление оказывают значительно меньщее вли-ие на величину выходного напряжения, чем в неинвертирующем. Так как акцию ОУ на си7[фазные сигналы принято характеризовать коэффициентом лабления синфазного сигнала Кос ~ с, перепишем неравенства (1 16): Кос и> Ru/Rny, <ос н (R; Rn)lR. 1едовлтельЕ10, в инвертирующем включении существенно лучше ослабля-ря синфазное входное напряжение. Таким образом, ОС улучц1ает не только статические (Rbk- вых, ос). ) и эксплуатационные (уменьшается влияние R[) показатели неи.т,еальности У) - 1.2, Статические показатели неидеальности и схемотехнические методы их улучшения Действие статических показателей проявляется в том, что при эвных потенциалах входов выходное напряжение ОУ отличается г нуля*. Все статические ош1-гбки, обусювленные статическими эказателями неидеальности, приводят ко входу ОУ [10- 121: - d/, + d[p)/dT\ АСцих - динамический диапазон выходного апряжения; 0 - синфазное входное напряжение; ДСп - не-табильность напряжения питания; Rn, Rr2 ~ сопротивления сточников входных сигналов; б( - временной дрейф. Здесь и далее, Кроме специально оговоренных случаев, предполагает-я, что напряжение питания ОУ симметрично (например, гЬ 15 В). Определяющим величину суммарной статической ошибки чаще всего выступает слагаемое Е, по величине которого можно судить о качестве входного каскада ОУ (табл. ).3). Известные схемотехнические методы уменьшения Е. сводятся к компенсации U н ьходных токов в диапазоне рабочих температур аппарат}ры. /ne/tnepamffpbf 12.]. Напряжение смещения нуля, его температурный дрейф и методы их уменьшения Напряжение /У -. которое необходимо приложить от источников с Rn -- (-2 = О к одному из входов ОУ для получения на выходе нулевого погенциала, называется напряжением смещения нуля*. Основным источником этой ошибки является входной дифференциальный каскад (ДК) АИС. Во входных каскадах современных АИС применяются чаще всего биполярные транзисторы (БТ), работающие в микрорежиме. Полевые транзисторы (ПТ) применяются реже, так. как ©ни ил;ею7 значительно большие величины и его дрейфа по сравнению с ДК на БТ (табл. ГЗ). Это объясняется в первую очередь большим разбросом напрмжен-ий исток - затвор ПТ, который достигает десятых долей вольта. В ДК на БТ напряжение C, определяется в основном разбросом напряжений эмиттерно-базо-вых переходов входных транзисторов ДК Сем U.,Q2 - Сэб! ~ = ЛСэо- Температ\риый дрейф равен dUjdT U,oT. Подробный анализ факторов, определяющих и его дрейф, имеется в [1-81. Поэтому нине остановимся на менее известных аспектах техники уменьшения ошибок смещения в ОУ. Дрейф прогрева ОУ проявляется прн быстром изменении температуры. При этом Ui ьюжет быть больше значения, получаемого при медленном изменении температуры (рис. 1.3). Это явление связано с возникновением термических градиентов внутри подложки ИС как при включении питания ОУ или переключения нагрузки, так и при быстром изменении окружающей температуры. В первом случае мощность, рассеиваемая на выходе ОУ, быстро передается на его вход. Наибольшее влияние разницы температур проявляется в парных транзисторах ДК, где она нарушает баланс дрейфов их  Рис. 1.4 Иэмеиеине ргапряжения смешения нуля при медленном и быстром изменении температуры Ч Другой вход при этом заземляется! Параметры ОУ

эмиттерно-базовых напряжений (плн напряжений исток-затвор)*. Кроме дополнительного увеличения Сс. это создает иллюзию бесконечного коэффициента усиления ОУ или эффект отрицательного выходного сопротивления схемы [8], Кристаллы полупроводниковых ОУ имеют достаточно малые размер-ь1 и высокую однородность структур, обеспечивая в завнси- . --- \ При разности температур транзисторов, равной долям градуса, значи- * гельно превышается обычное значение дрейфа Ucu ДК на БТ порядка 3 мкВ/°С,

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||