| |

|

Главная

>

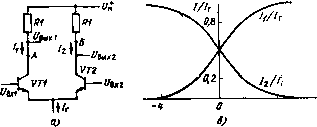

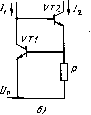

Источники и стабилизаторы тока источники-стабилизаторы тока-напряжения Современные АИС имеют сравнительно сложную схемотехнику, основанную на достижениях полупроводниковой технологии. Однако, как показывает опыт, разработчику МЭА не обязательно знать все тонкости схемотехники и технологии изготов- ления АИС. Вместе с тем, не зная общих принципов их построения и современной номенклатуры, трудно ожидать создания надежной МЭА с предельным сочетанием точности, быстродействия и потребляемой мощности. Поэтому в этой главе дается общее представление о структурах основных типов АИС, их основных параметрах, особенностях применения, оценивается их технический уровень и описываются возможные направления развития. 1.1. ЭЛЕМЕНТЫ СХЕМОТЕХНИКИ АИС Особенности схемотехнических решений, используемых для построения АИС, обусловлены следующими ограничениями в технологии изготовления ИС: большими разбросами абсолютных значений параметров элементов, микронными размерами элементов, трудностью технологической совместимости различных активных элементов, отсутствием индуктивности среди элементов ИС. В ИС выгодно применять активные элементы вместо пассивных, занимающих большую площадь кристалла. Элементы, расположенные на кристалле рядом, имеют практически одинаковые параметры. Разработчики АИС проектируют их таким образом, чтобы в максимальной степени использовать преимущества полупроводниковой технологии и свести к минимуму влияние ограничений, накладываемых этой технологией. Основным схемотехническим узлом АИС является дифференциальный усилитель ДУ (рис. 1.1,а). Симметрия ДУ относительно генератора постоянного тока /г делает его схему идеальной для применения в АИС, так как ДУ усиливает рассогласование между параметрами элементов плеч VT1, R1 и VT2, R1. Вследствие того ДУ часто называют балансным или разностным (усилитель разницы между двумя сигналами, поданными на входы ДУ). Если 6вх1 = 6вх2, т. е. изменения входных сигналов совпадают по фазе и одинаковы по амплитуде, то токи в плечах ДУ постоянны, равны и ивых1 = и.вых2 = и+ -1гЯ\12. Одинаковые входные сигналы ДУ называются синфазными, а ДУ тем лучше, чем меньше изменение А/вых.с= tBbixi-t/Bbix2 вызывает изменение t/Bxi(t/Bxi = bBx2). В реальном ДУ из-за разбаланса плеч, т. е. разброса параметров резисторов и транзисторов, а также конечного значения выходного сопротивления генератора тока /г при Ubx.c = Ubxi = Usx2 имеем Аивых.сфО. Отношение А/вых.о/вх.с называется коэффициентом усиления синфазного сигнала.  Рис. 1.1. Дифференциальный усилитель (а) и его вольт-амперная характеристика (б) Если t/axi-/вх2 = /вх.д=70, Т. 6. ИЗ ВХОД ДУ подано дифференциальное напряжение {/вх.д, то происходит перераспределение токов между плечами каскада, но сумма токов /i+/2 = /r остается постоянной. Учитывая, что /i = /ko exp(t/3.6i/9T), а /2 =/ко ехр (/эбг/ фт), где /ко - тепловой ток обратно-смещенного эмиттерно-базо-вого перехода; фт [7К/11 600] В - температурный потенциал, получаем /i = /n/i[l+exp(-(/в.д/фт)] и /2 = /г/[1+ехр(гУвх.д/фг)],. Здесь /вх.д= /э.б1-/э.б2. Зависимости токов /1 и h от Ubx.a показаны на рис. 1.1,б. Крутизна ДУ, а следовательно, и его коэффициент усиления Ки достигают максимального значения при (/вх.д~0, т. е. при очень малых входных сигналах. В этом нетрудно убедиться, определив производную d/r/dt/вх.д и приравняв ее нулю. Максимальное значение крутизны ДУ SdhldUBx.n для дифференциального выхода равно hlT- Следовательно, Ku = SRi = = /г/?1/2фг. Из рис 1.1,6 видно, что в ДУ значение S близко к максимальному при I /вх.д <С2фг, а уже при 6вх>4фг усиление t/вх.д практически отсутствует, так как в этом случае перераспределения токов в плечах практически не происходит. Как видно из выражения для Ки, его можно увеличить, только увеличив ток /г и сопротивление нагрузки. Однако в первом случае увеличивается входной ток ДУ /вх = /г/2/121э, где Нэ - коэффициент передачи базового тока транзистора, что нежелательно, так как уменьшается входное сопротивление ДУ. Во втором случае увеличивается площадь резисторов на кристалле и возрастает требуемое напряжение витания [/+п для сохранения активного режима работы транзисторов VT1, VT2, что также недопустимо. Решением проблемы является замена резисторной нагрузки транзисторной. Простейшая структура транзисторной нагрузки показана на рис. \.2,а. Этот узел называют отражателем тока, или токовым зеркалом. Ток в отража-  Рис. 1.2. Отражатель (а) и генератор (б) тока Рис. 1.3. Схемы сдвига постоянного напряжения на стабилитроне (а) и резисторе (б) теле задается по цепи транзистора VTa. Если транзисторы идентичны, а /г21э-оо, то справедливо равенство 6э.бА = фт ln(/i Ko) = =1э.б£ = фг1п(/2 ко), где Уэ.бА и (/э.бв-соответственно падения аапряжения на эмиттерно-базовых переходах транзисторов VTa и VT. Очевидно, что записанное равенство справедливо при Ii = h. Структура ДУ с активной транзисторной нагрузкой, подключаемой 9 точках А и Б схемы на рис. 1.1,а вместо резисторов, является основной в операционных усилителях (ОУ). Для задания тока /г в ДУ используются транзисторные генераторы тока (ГТ). Одна из наиболее распространенных в АИС структур ГТ показана на рис. 1.2,6. По существу -это модифицированная схема отражателя тока, в которой VTa заменен резистором R, а VT2 включен в цепь ОС. Выходом ГТ является коллектор транзистора VT2, ток через который /2 = t/a.ei/i?, где 1.61 = = pr!n(/i Ko) Выходное сопротивление такого ГТ изменяется от 5-10 до 10 кОм в зависимости от значения h и параметров транзисторов. Дифференциальные усилители используют на входе АИС. В качестве промежуточных усилительных каскадов применяют либо ДУ, либо усилители, выполненные на транзисторе с общим эмиттером. Нагрузкой такого транзисторного усилителя, как правило, является ГТ с большим выходным сопротивлением [1]. Для согласования уровней выходных сигналов ДУ с напряжениями смещения на входах промежуточного усилителя в АИС используют схемы сдвига уровня, выполненные на базе эмиттерных повторителей (рис. 1.3). Схема на рис. 1.3,о: обеспечивает сдвиг уровня t/вх, равный t/cflB= t/s.a+t/cT, где Uct - падение напряжения на стабилитроне. В схеме на рис. 1.3,6 UcnB= Ua.e+hR и может регулироваться изменением R или /г. Недостатками этой схемы являются большее, чем у первой, выходное сопротивление, равное

|