| |

|

Главная

>

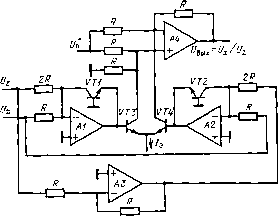

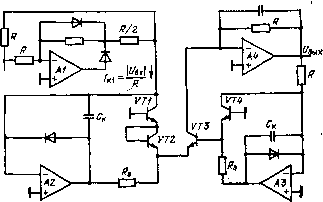

Источники и стабилизаторы тока Точность перемножения можно повысить до 0,5% (типовое значение 2%), уменьшив токи /3 до 0,8 мА и ограничившись диапазоном входных сигналов ±5 В. Последнее достигается в основном благодаря уменьшению нелинейных искажений в логарифмирующих и антилогарифмирующих каскадах схемы. Быстродействие 525ПС1 можно повысить, подключая к его выходу широкополосный ОУ, преобразующий дифференциальный сигнал тока в напряжение (рис. 2.26). Сопротивление резистора Rh выбирается так, чтобы при изменениях выходного тока в диапазоне ±0,2 мА относительно своего типового значения 1 мА транзисторы работали в линейной области. Для получения минимальной погрешности перемножения транзисторы в парах должны быть идентичными. Выбор усилителя определяется требованиями к полосе пропускания всей схемы. Например, если необходима малосигнальная полоса пропуска 5 МГц, а частота, до которой сохраняется максимальный размах выходного напряжения схемы, 1,4 МГц, то ОУ должен иметь полосу пропускания на уровне единичного усиления не менее 10 МГц, а скорость нарастания выходного напряжения - около 100 В/мкс. Сопротивление Ro-c выбирается исходя из требуемого размаха выходного напряжения (i?o.c = 25 кОм для [/вых=±: ±10 В). Деление двух аналоговых сигналов можно осуществить, включив перемножитель в цепь ОС усилителя [2]. Однако в этом случае, во-первых, деление возможно только в двух квадрантах, поскольку Ux и Uy должны иметь противоположную полярность для сохранения отрицательной ОС, а во-вторых, при малых входных напряжениях погрешность возрастает. Деление сигналов можно выполнить и с помощью перемножителя 525ПС1, управляя величиной тока /3. В этом случае {/вых= к выходу 680 к. 5г5ПС1  Рис. 2.26. Схема увеличения быстродействия перемножителя 525ПС1 Рис. 2.27. Делитель на ОУ (А/-Л4-1401УД2) и дифференциальном каскаде = KUxUy/Uz, где Uz является функцией от тока Iz={Uz-- ~Ua.&)l{Rz + 0,b kOm)===[/z/14,3 kOm+1 mA. При Ux=Uy = b В нормированное относительно тока 1 мА выходное напряжение [/вых = = 2,31 з, где ток /3 - в миллиамперах. Начальный сдвиг выходного напряжения устраняется вишней регулировкой. Аналоговые делители на перемножителях имеют обычно точность не лучше 5%, которая сохраняется в сравнительно узком диапазоне изменения амплитуды входных сигналов. Поэтому разработаны специализированные аналоговые делители, лучшие из которых построены по методу переменной крутизны и на логарифмических усилителях [48]. В делителе, построенном по методу переменной крутизны (рис. 2.27), напряжение подается на два идентичных усилителя А1 и А2. Сигнал Uz и сигнал -Uz, проинвертированный A3, прикладываются в суммирующие точки тех же усилителей. Напряжения Ux и Uz преобразуются в токи, которые суммируются и вычитаются усилителями А1 и А2. Напряжения Ux и Uz пропорциональны логарифмам суммы и разности этих токов. Транзисторы VT3 и VT4 дифференциального антилогарифмического усилителя преобразуют разность коллекторных токов в напряжение [/вых = А/к2/?о с, где Д/к = Ш2/.; Iz=Uz/2R; Ix=UxJR. Поэтому UBb,x = 2hRo.cUzlVx. Точность деления такой схемы существенно зависит от параметров ОУ. Поскольку входные токи большинства ОУ -порядка 100 нА, они существенно ограничивают динамический диапазон входных сигналов, который мог бы определяться диапазоном идеальности вольт-амперной характеристики р-п-перехода, равным 10 нА - 100 мкА. Несколько лучшие результаты можно получить, используя ОУ с полевыми транзисторами на входе, сохраняя постоянной температуру и вводя регулировку смещения нуля усилителя. Симметричная структура схемы обеспечивает ее работу в двух квадрантах. При идеально сбалансированных токах в симметричных цепях нелинейные искажения отсутствуют. Балансировку можно провести, подбирая сопротивления входных резисторов. Если диапазон изменения значений делителя ограничен напряжениями 10 мВ-1 В, то, используя 1%-ные резисторы, можно получить точность около 1%. При токе /э=0,2 мА и использовании ОУ 1401УД2 или аналогичных по параметрам полоса пропускания - около 0,5 МГц. Полоса пропускания расширяется более чем на порядок в случае применения ОУ 154УДЗ и большем токе /оп- 2.5. ВЫДЕЛЕНИЕ СРЕДНЕГО КВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ Простую схему выделения среднего квадратического значения сигнала можно построить на базе счетверенного ОУ 1401УД2 (рис. 2.28). Схема состоит из четырех функциональных блоков: выделителя абсолютной величины сигнала на базе А1, логарифмического усилителя на А2, антилогарифмического усилителя и интегратора-сумматора на А4. Необходимо выделение абсолютной ве-98 личины сигнала, так как логарифмический усилитель обрабатывает только положительные сигналы. Схема на А1 преобразует входное напряжение в ток /к= \Ubx\IR, протекающий в коллекторной цепи транзистора VT1. На коллекторе этого транзистора напряжение поддерживается близким к нулю с помощью А2.  Рис. 2.28. Схема выделения среднего квадратического значения с помощью счетверенного ОУ В цепь обратной связи А2 включены два транзистора, чтобы получить удвоенный логарифм от тока /к, т. е. возведение в квадрат входного напряжения. Затем выходное напряжение А2 поступает на антилогарифмирующий усилитель, а точнее на эмиттер транзистора VT3, включенного в цепь обратной связи A3. Если в качестве VT1, VT4 и VT2, VT3 использованы идентичные по параметрам транзисторы, то справедливо равенство [/э.б1-Ь[/э.б2= э.бз--Ч-t/э.б 4, где f/э.б i-fa.e 4 - соответственно эмиттерно-базовые напряжения VT1-VT4. Тогда токи, протекающие через транзисторы, будут связаны соотношением /k3=/ki/k2 k4, где /к1-/к4-соответственно токи через транзисторы VT1-VT4. Последнее равенство будет тем точнее, чем больше /i2ia транзисторов и чем меньше входные токи ОУ коллекторных токов транзисторов. Поскольку через транзисторы VTJ и VT2 протекает одинаковый ток, равный (к\ = 1к2= \Ubx\IR, то [/вых=/кз/ = У С?вх. Диоды в цспях обратной связи А2 и A3 исключают обратное смещение эмиттерно-базовых переходов транзисторов напряжением, большим 0,7 В. Назначение и выбор сопротивления Rg и емкости Ск описаны в § 2.2. 2.6. ИНТЕГРАТОРЫ Интегрирование аналоговых сигналов осуществляется ОУ с емкостной ОС (рис. 2.29). Благодаря большому коэффициенту усиления и малому входному току напряжение на инвертирующем входе усилителя близко к нулю, а токи во входной цепи /г и 4* Зак. 121 99

|