| |

|

Главная

>

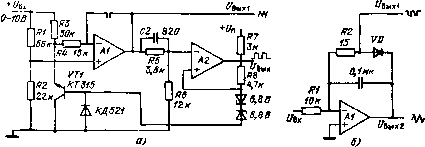

Источники и стабилизаторы тока ОС компаратора. Эмиттерный ток насыщенного транзистора VT3, приблизительно равный 11 мА, поступает в суммирующую точку компаратора, поддерживая тем самым напряжение на неинвертирующем входе на уровне потенциала земли. При этом напряжение на выходе интегратора начинает быстро убывать (по модулю). Когда потенциал на инвертирующем входе компаратора достигает нуля, компаратор переключается и закрывает транзисторный ключ VT3. Затем цикл повторяется. Резистор R12 включен в схему для ограничения базового тока транзистора VT3; конденсаторы С5 и Сб ускоряют процесс включения - выключения этого транзистора. Время tl, в течение которого напряжение на выходе интегратора изменяется от О до -4 В, определяется постоянной времени RiCi и приращением амплитуды входного напряжения AUbx- t = RC,AU,JAU . (3.3) Время сброса интегратора 4 = С, (А V ,JI ) = Rn С, (А UJU-) (3.4) где AUbmx - максимальный размах напряжения на выходе интегратора; /к - коллекторный ток открытого транзистора VT3; U-n - напряжение питания. Для Af/вых справедливо следующее выражение: U.u.=Rioy7(Rio + n). (3.5) с помощью выражений (3.3) - (3.5) легко определить период генерируемых импульсов: Т = Q U-/{R +Rn)iRi/AU. + Ru/Un). Так как в данном случае справедливо неравенство RJA.UbxRw-: U~ii, выражение для определения частоты выходных импульсов можно представить в виде f~ {Rlo + Rll)Uвx/iRlR\oCU-a). Из этого выражения следует, что схема имеет линейную зависимость частоты / от входного напряжения с коэффициентом преобразования 100 Гц/В. В предыдущих схемах основной вклад в ощибку преобразования (нарушение линейности зависимости частоты выходных импульсов от входного напряжения) вносило отличное от нуля время разряда интегрирующего конденсатора, т. е. время сброса интегратора. Один из способов компенсации этого времени показан на рис. 3.6 [59]. -i-i . ут vn Схема работает с положительными М -Щ значениями входных наиряжений. ч-\ Справедливо следующее выражение для частоты следования выходных им- пульсов: /= 1/(714-Гг), где - время -1- -ffon интегрирования входного напряжения T r. f /I / т Рис. 3.6. Схема преобразовате- интегратором А1; Гг - время сброса компенсацией времени интегратора. Если оба ОУ имеют не- сброса интегратора значительные напряжения смещения нуля и малые входные токи смещения, условие для сброса интегратора может быть представлено в виде Uou=Oc + U2=[ + f-)u , (3.6) где Uc и Ur2 - падения напряжений на конденсаторе С и резисторе R2 соответственно; Uon - опорное напряжение. Если сопротивление R2 выбрать таким, чтобы постоянная времени R2C была равна времени сброса интегратора Гг, то выражение (3.6) преобразуется к виду Uou + и,.. = и,. или /= [/,вх = const. Таким образом, частота выходных импульсов преобразователя пропорциональна среднему значению входного напряжения Ubx даже в том случае, когда Ubx изменяется с высокой скоростью. Однако при компенсации таким способом времени сброса следует учитывать тот факт, что измеиение входного напряжения за время Гг приведет к ухудшению параметров схемы. Поэтому такая компенсация эффективна лишь при медленно изменяющихся входных управляющих сигналах. 3.1.3. ПРЕОБРАЗОВАТЕЛИ С ПОВЫШЕННОЙ ЛИНЕЙНОСТЬЮ Анализ простейших преобразователей напряжения в частоту показывает, что при построении схем с высокой линейностью передаточной характеристики необходимо руководствоваться следующими основными положениями: используемый в режиме интегратора ОУ должен иметь большой коэффициент усиления при разомкнутой петле ОС и высокое входное сопротивление; верхнее и нижнее зиачения порогового напряжения компаратора должны оставаться неизменными в процессе работы схемы, для чего следует применять высокостабилизированный источник отрицательного напряжения питания и ОУ с низким входным напряжением смещения и малым дрейфом; скорость нарастания выходного напряжения интегратора должна быть достаточно высокой, чтобы обеспечить быстрое время разряда интегрирующего конденсатора. Следует отметить, что выполнение последней рекомендации наиболее важно, поскольку время сброса вносит максимальный вклад в точность преобразователя. Ниже приведено несколько практических схем преобразователей напряжения в частоту с высокой линейностью, дан их краткий анализ. Особенность схемы преобразователя, изображенной на рис. 3.7,а, заключается в том, что времена заряда и разряда интегрирующего конденсатора С1 в схеме равны; это обеспечивает симметричность выходных импульсов и позволяет в определенных пределах ско мпенсировать время включения транзистора VT1, коллекторный ток которого разряжает этот конденсатор [60]. Для того чтобы времена нарастания и спада напряжения на выходе интегратора были равны между собой, необходимо выполнение условия /?i/i?2= 1+ /?з/?4. Однако в этом выражении не учтено с/ 100  Рис. 3.7. Преобразователи с линейностью передаточной характеристикой 0,1% (а) и 0,2% (б) отличное от нуля значение времени задержки включения транзистора VT1, которое может существенно нарушить симметрию выходных импульсов верхнего предела рабочего диапазона частот преобразователя (в данном случае 100 кГц). Кроме того, на таких частотах время задержки значительно ухудшит линейность преобразования. Для компенсации влияния транзистора VT1 на линейность ие-редаточной характеристики в схеме использована фазосдвигающая цепь R5C2R6, включенная между интегратором и компаратором напряжения. На низких частотах (при малых входных напряжениях) влиянием конденсатора С2 на выходной сигнал можно пренебречь, и фазосдвигающая цепь работает как обычный резисторный делитель. С повышением рабочей частоты сопротивление конденсатора уменьшается, и большая часть выходного напряжения интегратора поступает на вход компаратора, вызывая тем самым более раннее переключение последнего. При соответствующем выборе номиналов этой цепи задержка включения транзистора VT1 может быть полностью скомпенсирована. Использование транзистора VT1 в инверсном режиме также способствует повышению качества преобразования, поскольку при таком включении уменьшается падение напряжения коллектор - эмиттер транзистора в насыщенном состоянии. Предложенная схема имеет хорошие температурные характеристики, так как положительный температурный коэффициент по напряжению стабилитронов компенсирует отрицательный коэффициент прямо смещенных р-п-переходов транзистора. С номиналами элементов, указанными на рис. 3.7,а, при изменении входного напряжения от О до 10 В частота выходных импульсов изменяется от О до 40 кГц (линейность в пределах 0,1%). Следует отметить,

|