| |

|

Главная

>

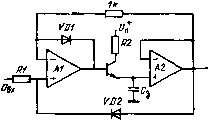

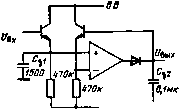

Источники и стабилизаторы тока Из-за действия этого напряжения замедляется разряд Сз, что приводит к появлению зоны нечувствительности амплитудного детектора вблизи нуля при быстром изменении циклов детектирования. Остаточное напряжение на запоминающем конденсаторе Сз по существу является ложным первым экстремумом анализируемой входной функции. Для уменьшения остаточного напряжения выход усилителя А! шунтируют дополнительным полевым транзистором, работающим синхронно с VT1. Благодаря этому выходной ток А1 не протекает через VT1, пока напряжения на выходе А1 меньше напряжения на открытом диоде VD1. В такой схеме типы транзистора и усилителя необходимо выбирать исходя из минимального значения сопротивления открытого транзистора и максимального выходного тока ОУ. Остаточное положительное напряжение сброса можно также устранить, если Сз разряжается до отрицательного напряжения. В этом случае амплитудный детектор реагирует на максимум положительного напряжения любой амплитуды. Уменьшение ошибок и времени выборки. Статические ошибки выборки обусловлены действием статических показателей неидеальности ОУ, методы улучшения которых описаны в гл. 1. Динамические ошибки выборки возникают в первую очередь из-за ограниченной скорости нарастания выходного напряжения усилителя и выбросов переходного процесса при заряде Сз. Время выборки амплитудного детектора - это минимальное время, необходимое для перехода из режима хранения в режим слежения за входным сигналом с заданной точностью. Это время определяется длительностью заряда запоминающего конденсатора и установления выходного напряжения с заданной точностью. Если это время будет больше, чем длительность .максимума входного сигнала, то амплитудный детектор не зафиксирует его действительной величины. Скорость заряда, ограниченную конечным выходным током ОУ, нетрудно увеличить, заменив диод VD1 в схеме на рис. 5.14,а транзистором (рис. 5.15). Ток через транзистор ограничивается резистором R2. При уменьшении входного сигнала эмиттерно-базовый переход транзистора смещается в обратном направлении, так как напряжение на эмиттере фиксируется конденсатором, а на базе оно уменьшается. Для исключения пробоя эмиттерио-базового перехода между выходом А1 и базой транзистора следует включить резистор сопротивления 1 кОм. Для увеличения быстродействия иногда ограничивают размах входного сигнала А1. Это достигается включением в схему дополнительной цепи общей отрицательной ОС на диоде и резисторе R1 (см. рис. 5.15). При уменьшении входного сигнала дифференциальное напряжение на входе А1 не может превысить падение напряжения на диоде VD2, а напряжение на неинвертирующем входе А1 меньше напряжения на Сз на величину С/д. Таким образом, для фиксаций нового максимума выходное напряжение А1 должно измениться только на З/д. Благодаря этому значительно 172 увеличивается разрешающая способность детектора по длительности экстремумов и уменьшается напряжение на обратно-смещепном эмиттерно-базовом переходе транзистора, а следовательно, и ток утечки через него [89].   -1ZB Рис. 5.15. Быстродействующий двухкаскадный амплитудный детектор Рис. 5.16. Быстродействующий амплитудный детектор с покаскадным запоминанием Скорость заряда Сз можно увеличить, исключив влияние цепи корректирующей АЧХ ОУ на время заряда Сз. Когда все диоды закрыты, цепь ОС усилителя А1 разомкнута. Для ОУ с разомкнутой ОС не требуется цепь частотной коррекции с большими емкостями, и благодаря этому можно обеспечить значительно большие скорость нарастания выходного напряжения и усиление на высоких частотах. В этом случае к усилителю Al подключается корректирующий конденсатор только после завершения выборки сигнала с точностью ± [/д, т. е. после смещения VDI или эмиттерно-базового перехода транзистора в прямом направлении. Детектор коротких импульсов. Может регистрировать пики входного сигнала длительностью Ги>-20 не и амплитудой от 50 мВ до 5 В (рис. 5.16). В этой схеме входной сигнал запоминается на короткое время t\ на конденсаторе Сз1 с небольшой емкостью, которую можно зарядить за время Ги. Затем за время /г заряжается до величины [/вх конденсатор Сзг с большой емкостью, который и обеспечивает точное и длительное хранение [/вх До поступления следующего пика сигнала на вход устройства. Точность работы схемы зависит в первую очередь от разряда Csi за время /г- Частота повторения пиков сигнала /вх не должна быть больше I 2, чтобы избежать увеличения динамической ошибки. Для исключения заряда запоминающего конденсатора до значения, превышающего значение экстремума [/вх, необходимо свести к минимуму выбросы переходных процессов. Для устранения этой ошибки входной усилитель должен иметь минимальную колебательность переходного процесса, что достигается правильным выбором параметров цепей, корректирующих его амплитудно-частотную характеристику. Обычно ОУ с внутренней коррекцией имеют колебательную переходную характеристику при подключении к их выходу конденса- тора большей емкостью. Поэтому желательно применять усилители с внешней 1Коррекцией, допускающие подстройку переходной характеристики. При этом выбор параметров корректирующей цепи осуществляется по виду переходного процесса при подаче иа вход амплитудного детектора (без диода VD1) ступеньки напряжения (см. гл. 1). Влияние большой емкости Сз можно уменьшить, включив резистор с небольшим сопротивлением (10-50 Ом) между выходом А1 и Сз или последовательно с Сз [90]. Любую из рассмотренных схем можно использовать для построения амплитудных детекторов, обеспечивающих усиление входного сигнала, которое получается добавлением резистора R1 в цепь обратной связи (см. рис. 5.14,а). В результате этого в режиме выборки схема представляет собой неинвертирующий усилитель с коэффициентом передачи {R2 + R1)IRi. Изменяя полярность включения диодов в рассмотренных схемах, получаем запоминание минимальных значений Ux- Двусторонний амплитудный детектор. Один из способов построения двустороннего амплитудного детектора состоит в совмещении детекторов, предназначенных для обработки положительного и отрицательного напряжений. Однако в этом случае потребовались бы четыре ОУ. Кроме того, на выходе можно получить только дифференциальный сигнал, для объединения которого необходим пятый ОУ. Более простая схема двустороннего амплитудного детектора показана на рис. 5.17. Здесь выходной сигнал снимается относи- 5,1к RZ 5,1к Vn3 iK RI 5,1к RZ 5,lK R1 Ik rz-Mjl. R1 5,1 к Ъ [>ис. 5.17. Двусторонний амплитудный детектор Рис. 5.18. Детектор абсолютных значений экстремумов гельно уровня земли, а компенсация разряда запоминающих кон-тенсаторов осуществляется в режиме хранения. Амплитудный де-гектор положительного сигнала выполнен на усилителе А2, дио-тах VD1 и У02 и конденсаторе CL Уменьшение в два раза сиг-1ала на входном резисторном делителе R1 компенсируется далее .силителем A3, так что общее усиление входного сигнала равно единице. Усилители A3 и А1 вместе со своими элементами в цепях ЗС реализуют инвертирующий амплитудный детектор отрицатель-юго сигнала. В этой схеме выход детектора положительных сиг-

|