| |

|

Главная

>

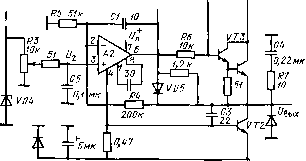

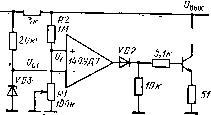

Источники и стабилизаторы тока 6.3.1. ЛИНЕЙНЫЕ СТАБИЛИЗАТОРЫ Рассмотренные выше источники опорного напряжения на ОУ по существу являются линейными стабилизаторами с очень жесткой характеристикой регулирования. Простейшая схема линейного стабилизатора показана на рис. 6.7. Опорное напряжение выбрано значительно меньше выходного для того, чтобы упростить реализацию единичного коэффициента усиления ОУ, необходимого для максимальной стабильности выходного напряжения. Максимальный выходной ток стабилизатора определяется коэффициентом передачи базового тока /i2i3 транзистора VT1 и выходным током, который может отдать операционный усилитель /вых тах/оу max/l2l3. ПрИ ЭТОМ МОЩНОСТЬ, рассеиваемая на транзисторе VT1, не превысит максимально допустимой величины Pyrimax, ССЛИ РуГ1 тах> ( вх - вых) X Х/вых max. Выходное напряжение определяется делителем R1, R2. ток через который задает резистор в соответствии с равенством /д = ст ?2. Поскольку входной ток ОУ мал, весь ток /д протекает через делитель R1, R2 и выходное напряжение С/вых= С/ст(1+ +/?i ?2). Обязательная в каждом стабилизаторе цепь защиты от короткого замыкания строится здесь на .EiiI I 1 транзисторе VT2 и резисторе R3. Цепь А защиты срабатывает в момент выполне- U ния равенства э.б1 = /вых/?з. При этом J транзистор VT2 открывается, от ОУ от- бирается дополнительный ток и его выходное напряжение падает. Пульсации выходного напряжения, возникающие в основном из-за конечного значения коэффициентов ослабления синфазного сиг-Рис. 6.7. Простейший- ли- 3 и подавления нестабильности на-нейный стабилизатор пряжения питания ОУ, частично отфиль- тровываются входным конденсатором. Хотя значения этих пульсаций для данной схемы не превышают нескольких десятков милливольт, в некоторых случаях и этого оказывается много. Недостатком использованной в схеме цепи защиты от короткого замыкания является сравнительно большое сопротивление R3, необходимое для получения падения напряжения Ua.ei транзистора VT2. Этот недостаток можно устранить, применяя вместо транзистора VT2 компаратор напряжения, способный различить изменение напряжения на R3, равное 10 мВ. Благодаря этому сопротивление R3 можно уменьшить в 100 раз, уменьшив тем самым выходное сопротивление стабилизатора. Схема функционально законченного линейного стабилизатора приведена на рис. 6.8 [97]. Стабилизатор состоит из источника опорного напряжения на транзисторе VT1, регулятора выходного напряжения вых на ОУ 140УД14 и цепи защиты от перегрузки по выходному току на ОУ 153УД6. Источник опорного напряжения  формирует различные напряжения для цепи защиты от перегрузки и регулятора [/вых. Опорное напряжение Ui в цепи защиты формируется стабилитроном VD1, ток через который равен -Uct)IRi. Выходной ток, при котором сработает цепь защиты, определится сопротивлением R2 и напряжением на инвертиру- KZ7/ Ri 5,iK ЩЪО VB3 (72 ZOO RZ 0,1  Un-S-iOB Рис. 6.8, Прецизионный линейный стабилизатор {VD2, VD3-2DC627) ющем входе А1. Если напряжение на неинвертирующем входе А1 больше, чем на инвертирующем, то на выходе этого ОУ устанавливается высокий потенциал, диод VD2 закрывается и А1 не влияет на работу регулятора. Выходное напряжение регулятора с мощным выходным транзистором VT3 изменяется с помощью резистора R1. Стабилитрон VD4 и резистор R3 образуют цепь, формирующую опорное напряжение регулятора. Коэффициент усиления регулируемого с помощью R3 опорного напряжения U2 равен .4/5- При отсутствии перегрузки по выходному току UBux=U2Ri/R5. Транзистор VT2 обеспечивает некоторый ток в выходном транзисторе VT3 при отключенной нагрузке. Диод VD3 включен в цепь коррекции амплитудно-частотной характеристики А1, чтобы напряжение на выходе Л/ поддерживалось примерно равным потенциалу на базе VT3. Благодаря этому время срабатывания цепи защиты не превышает нескольких микросекунд. В момент срабатывания защиты загорается светоиндикаторный диод VD5. Для устранения самовозбуждения стабилизатора в схему введены корректирующие конденсаторы С1-С4 и резисторы R6, R7. Указанные в схеме значения корректирующих элементов зависят от типа мощного выходного транзистора и конструктивного исполнения стабилизатора. При выборе типа транзисторов VT3 необходимо принимать во внимание то, что максимальный выходной ток А2 примерно равен 5 мА. Напряжение стабилитрона VD1 выбирается исходя из равенства (/ст = /?2/н max, ГДС /н max - МаКСИМаЛЬНО ДОПУСТИМЫЙ ВЫХОДНОЙ ТОК стабилизатора. Конденсатор С5 на входе А2 включен для уменьшения влияния высокочастотных флуктуации Uz на величину и вых. с помощью усилителя и сравнительно низковольтного транзистора можно осуществить стабилизацию напряжения, равного сотням вольт (рис. 6.9). Обойтись низковольтным транзистором позволяет стабилитрон VD1, на котором гасится значительная часть напряжения питания. Выходное напряжение делится резисторами R1, R2 и подается на вход ОУ. Последний сравнивает напряжения Ui и С/ст и обеспечивает выполнение равенства UiUcj. Диод VD2 предохраняет от обратного пробоя эмиттерно-базовый переход транзистора VT1. В нормальном режиме работы схемы диод VD2 смещен в прямом направлении и в базу транзистора VT1 течет необходимый ток. Для указанных на схеме значений элементов коэффициент стабилизации выходного напряжения равен 0,04% прп изменении выходного тока от нуля до максимальной величины. Выходное напряжение С/вых = С/ст(1+/?2 ?1). Преиму-схемы - простота, а ее недостаток - большое 14 УЛ}  рис. 6.9. Высоковольтный стабилизатор напряжения щество описанной выходное сопротивление. Массовое применение в современной аппаратуре АИС, требующих одинаковых по абсолютной величине отрицательного и положительного напряжений питания, обусловило создание специальных стабилизаторов с дифференциальным и симметричным выходами. Наиболее удачная схема стабилизированного источника питания аналоговых микросхем с разнополярными равными питающими напряжениями представлена на рис. 6.10. Точное слежение одновременно за обоими выходными напряжениями обеспечивается использованием общего источника опорного напряжения стабилизатора. В верхней части схемы, вырабатывающей положительное напряжение, усилитель Al работает в режиме повторителя напряжения С/ст. Составные транзисторы VT1 и VT2 получают напряжение смещения от соответствующего нестабилизированного входного напряжения. Регулирование выходного напряжения транзистора VT1 осуществляется выходным сигналом усилителя Al. Усилитель А2 в части схемы, вырабатывающей отрицательное выходное напряжение, работает как инвертирующий повторитель напряжения. Для приведенных сопротивлений резисторов разница выходных напряжений не превышает 50 мВ, а их пульсации меньше 192

|